If you made a mistake in your pin locations or want to change them in the future, you can directly edit the UCF file instead of using PACE. By double-clicking on Edit Constraints (Text) in the Processes window, you can see the format of the UCF file. In the Sources window, hit F5 to refresh, then expand the hierarchy for the switch module to see the new file, switch.ucf, that has been added to the project. You may be prompted to choose a Bus Delimiter choose the top option, XST Default:, and click OK. When you are done entering the pin information, click Save. Your list of ports should look like this when you are done. The other information (I/O Std., Drive Str., etc.) does not have to be filled in. You should see each pin location fill in with blue on the pin diagram to the right. Connect the pins to your module's ports by clicking in the Loc box next to each port and typing in the proper pin, as shown in the image below. Click the Package View tab at the bottom of this window to see a diagram of the unconnected pins on the FPGA.Įach component on the board is connected to a pin on the FPGA. On the left, the ports of your module will be listed, and on the right is a diagram of the FPGA. Click OK, then when prompted to add a UCF file to your project, click Yes.

To do this, click on switch.v in the Sources window, expand the User Constraints item in Processes and double-click on Floorplan IO - Pre-Synthesis. If you get compilation errors, resolve them (ask a TA for help if necessary) before continuing.įor the ports in the module (SWITCHES and LEDS) to control the components on the board, they must be connected to pins on the FPGA. The console should not display any errors under the HDL Compilation section, and a should appear next to Check Syntax. To "compile" your Verilog code, make sure the switch.v file is highlighted in the Sources window, expand the Synthesize-XST item in the Processes window and double-click Check Syntax. When you are finished, your module should look like this: When saving to a network drive, ISE prompts you for every file you are saving, even if it already exists, so just click Save when the dialog box appears.

XILINX ISE 10.1 WINDOWS 7 CODE

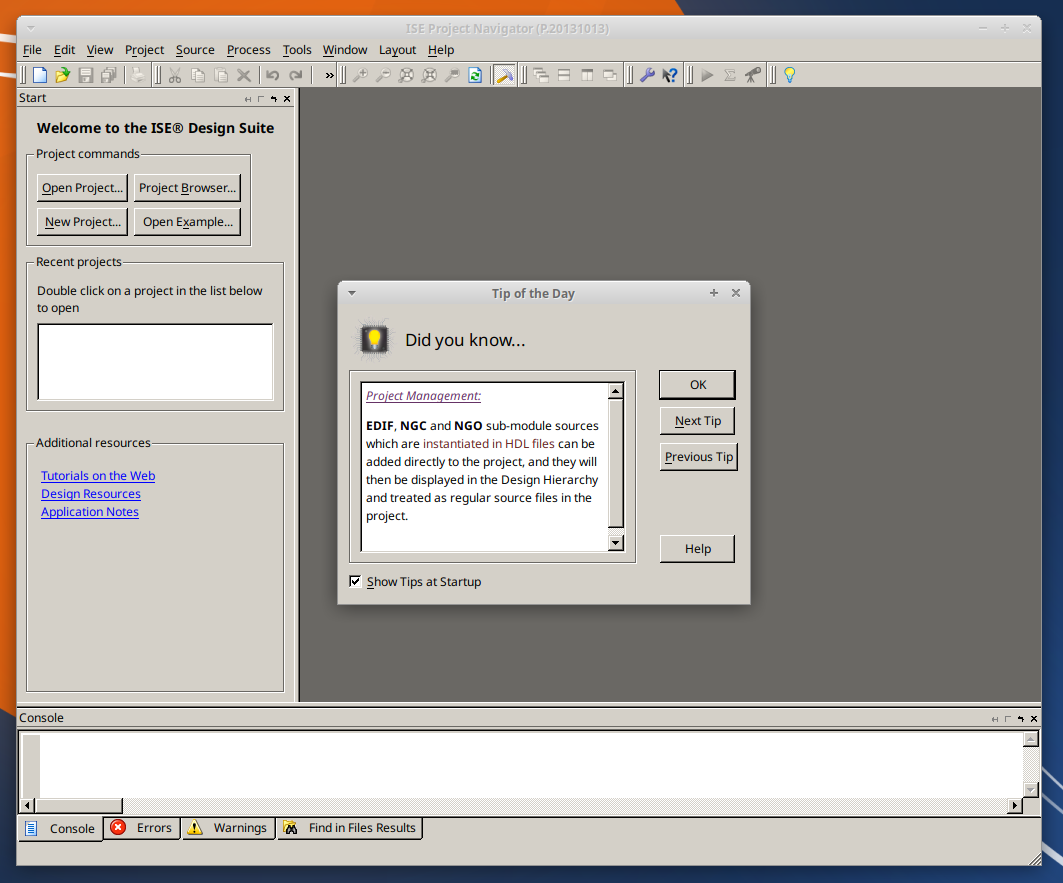

To connect the switches to the signals, just add one line of Verilog code to the module: The values of the switches are inputs to the module, and the signals to the LEDs are outputs from the module. The switch module will link the four user input switches on the board to the four LEDs next to the switches, so toggling the switches will turn the LEDs on and off. If this tab ever gets closed, you can open the file again by double-clicking on it in the Sources window. Select the switch.v tab in the editor window. The Design Summary tab on the editor window will be selected after you generate your new module for now, you can close this tab with the X button in the upper-right corner. There are four main windows in the Project Navigator: Sources, Processes, Console output, and the editor. Once your module is generated, the main ISE Project Navigator view appears. This screen takes your inputs and outputs and automatically generates A Verilog module is a self-contained hardware unit withĪn interface of inputs and outputs, which are specified on the next Module from the list and give the module the file name "switch", thenĬlick Next. On the next screen, click the New Source button.

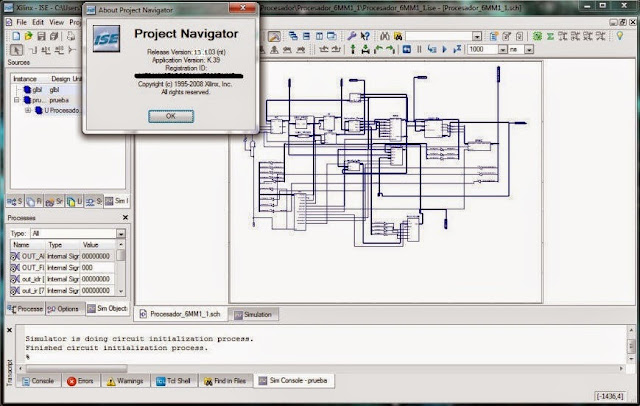

XILINX ISE 10.1 WINDOWS 7 SIMULATOR

(VHDL/Verilog)" and Simulator to "ISE Simulator" and click Next. Settings are Family = "Virtex2P", Device = "XC2VP30", Package = The following screen allows you to set the properties for the FPGA The Top-Level Source Type to HDL and click Next. Give the project a location on your mappedĮniac drive and enter a name for the project, such as "tutorial". Go to File -> New Project toĬreate a new ISE project. If so, closeĪn ISE project contains all the files needed to design a piece of First, ISE may have opened a previously used project.